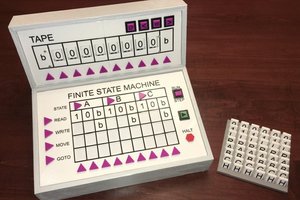

A state machine is a bit like a Rube Goldberg contraption. Something happens, which causes something else to happen, and so on. One of the first state machines I ever saw was made with timing motors and poker chips. A ringing phone would start the motors and the poker chips would push microswitches to start a tape player, then a tape recorder, and it made a crude answering machine. Our FPGA-based state machines will be more flexible and not quite as kludgy, but the principles will be the same.

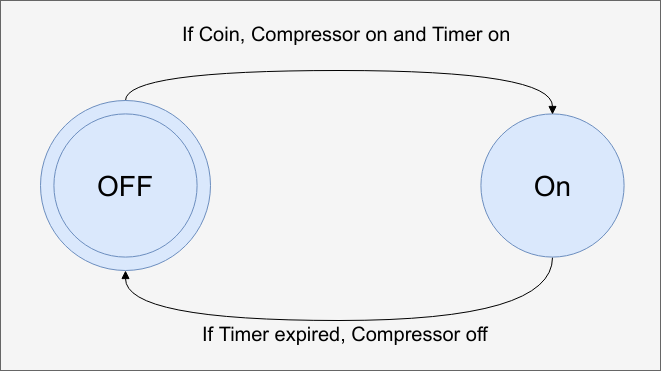

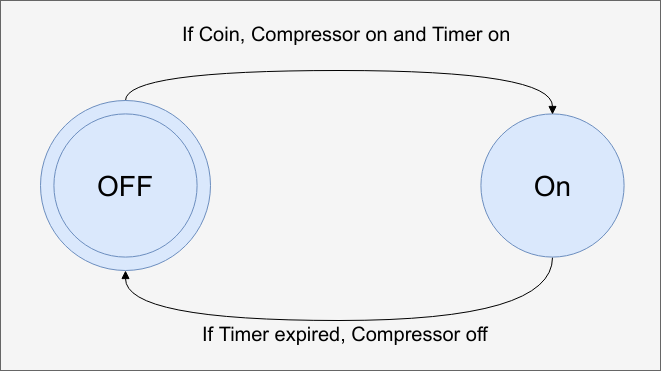

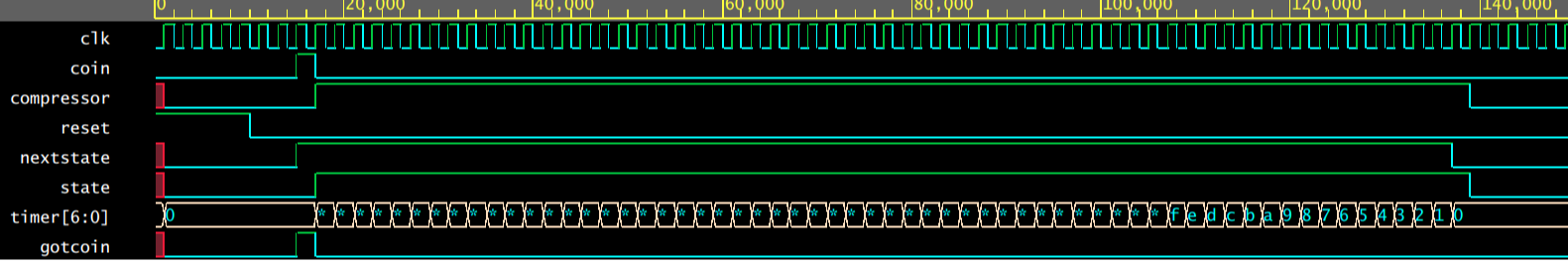

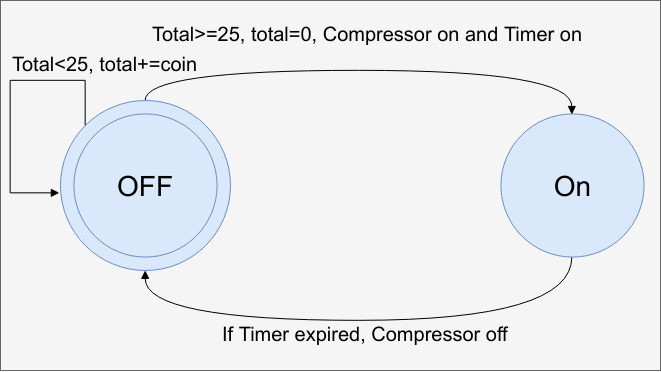

Let's take a really simple example. Suppose you have a machine that puts air in car tires at a gas station. There's a compressor, a timer, and a coin slot. When a quarter comes in the coin slot, you start the compressor and the timer. When the timer expires, you turn off the compressor. That's pretty simple, and you could probably do that with just some ad hoc logic. However, it could be a state machine. You'd only have two states: Off and On. When you are in the off state, you watch for a coin. When you see one, you go to the On state, turning on the compressor and the timer. Then you watch for the timer and when it fires, you turn everything off and go back to the off state.

A state diagram -- one we will look at in the Bootcamp -- might look like this:

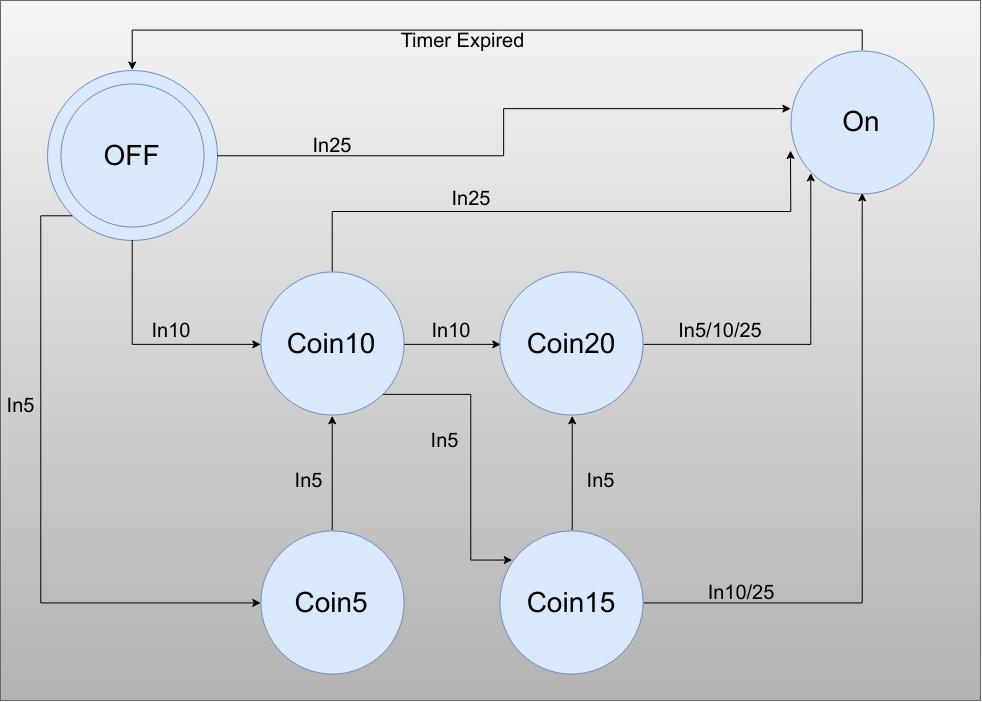

You might think that example isn't very useful, but consider this: What if next month, the price of air goes up to 75 cents and the coin slot will tell you if you got a quarter, a dime, or a nickle? Now it is harder to change an ad hoc design. What if while in the on state, the customer can add more coins to get more time in proportion to the coin they deposit? These would be easy things to handle in a state machine-based design.

You might think this is very different than using a CPU, but if you think about it, a CPU is just a very large state machine itself. Each instruction causes it to do different things depending on inputs and the previous state. Very few of our state machines will be that complex, though, unless you are building a CPU.

For this bootcamp, we'll assume you understand Verilog and the fundamentals of FPGAs. If not, you are in luck, because this bootcamp is part of a series:

| Bootcamp 0 | Covers basic digital logic concepts with simulations |

| Bootcamp 1 | Introduction to FPGA coding and simulation with combinatorial logic |

| Bootcamp 2 | More FPGA coding and simulation with flip flops (sequential logic) |

| Bootcamp 3 | Working with actual FPGA hardware |

| Bootcamp 4 | State Machines (this bootcamp) |

If you aren't comfortable with the basics, you can check out those bootcamps first and then return to this one when you are ready.

To start, look in the step-by-step instructions to learn about state machines with some hands-on exercises. You'll also find background articles in the project logs. You might want to browse them first and refer back to them as you work through the steps. The logs also have a glossary you can check for any unfamiliar terms.

Al Williams

Al Williams

Chris

Chris

Michael Gardi

Michael Gardi

Joseph Primmer

Joseph Primmer