Features

- Supports 3/4 lane MIPI DSI displays.

- DSI controller supports resolutions of up to 1080x1920 at 60 Hz refresh rate.

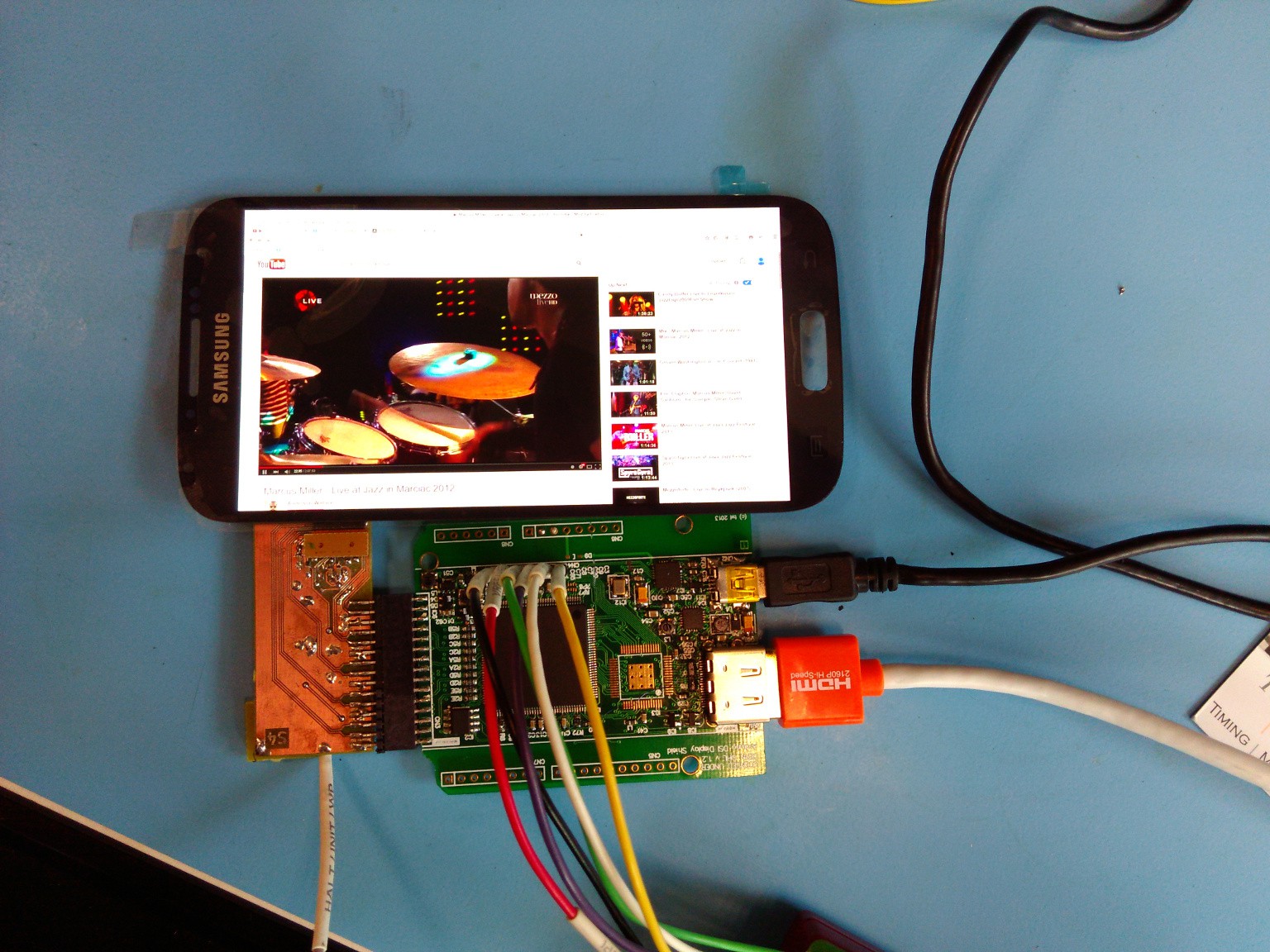

- Converts HDMI video to DSI - letting you connect any MIPI DSI screen to your PC, Raspi or similar devices. Conversion works up to 720p@60 Hz or 1080p@48 Hz.

- Built-in framebuffer with simple graphics stack, allowing to interface small microcontrollers, such as Arduino through 8-bit parallel or SPI busses

- Sub-$50 BOM, including 4-layer PCB (@100pcs).

- Powered through mini USB connector.

- Embedded 32-bit CPU, available for user applications.

Project history

- 12/2013: Schematics & PCB done.

- 12/2013: Initial version of the firmware, works with Iphone4/4s screens on a FPGA dev kit.

- 02/2014: Got the PCBs and components.

- 02/2014: Test PCB assembled, drive both 3- and 4-lane screens.

- 07/2014: Started work on HDMI <> DSI conversion.

- 08/2014: HDMI convesion working for 640x960 Iphone4 screen.

- 08/2014: DSI core achieves 1080p @ 60 Hz (48 Hz with HDMI conversion).

- 08/2014: Rev 1.1. PCB design, schematics and firmware released.

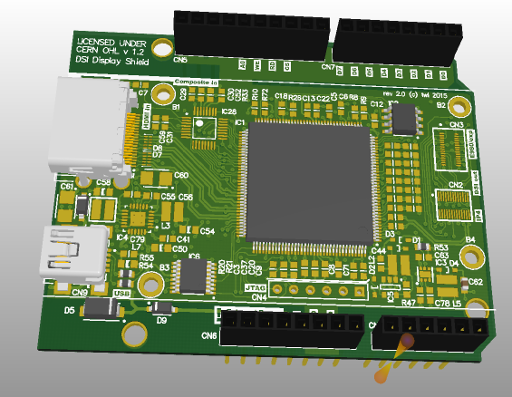

- 06/2015: Prototypingr rev 2.0.

To do

- Arduino interface/drawing commands (depending on demand).

- Test external HDMI decoder with displays larger than 1080p.

- Port Doom to run on the softcore CPU.

Hardware

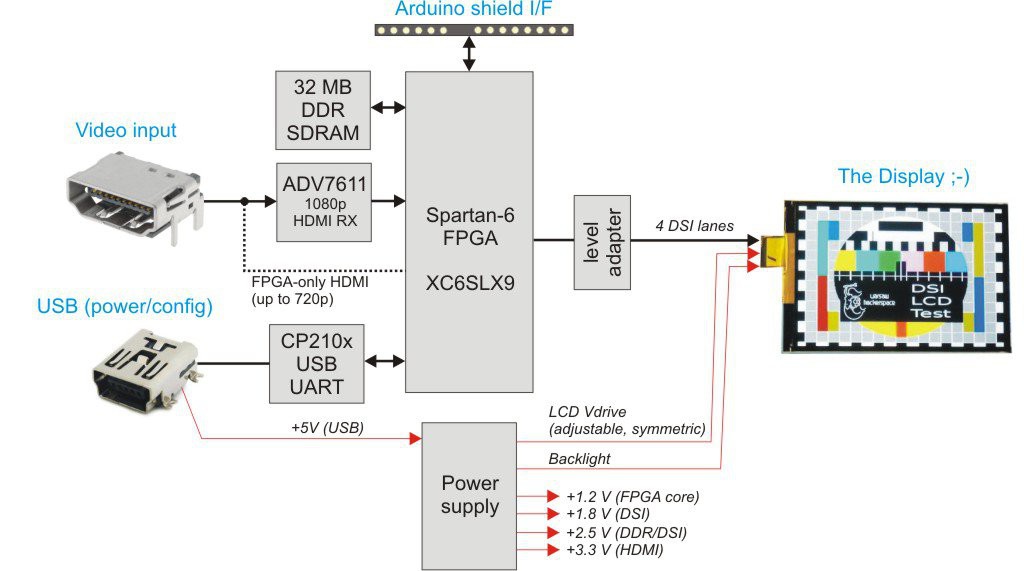

The diagram below shows the main blocks of the design:

- The FPGA: Xilinx Spartan-6-SLX9. Highlights: amateur-friendly TQFP144 package and built-in SerDes rated up to 1080 Mbits/s. The FPGA does pretty much everything in this project, hosting the MIPI DSI core, framebuffer controller with DDR memory, HDMI/DVI decoder. Everything is managed by an embedded Lattice Mico32 CPU.

- DSI Level adapter: a bunch of resistors interfacing the FPGA's 1.8 V SSTL/LVCMOS I/O to DSI levels. More info in the FPGA section.

- DSI connector: a standard 2x15pin 2mm pitch female connector with all DSI signals, power supplies and some GPIO pins for interfacing with the display. Since connector pinouts differ between displays the idea here is to use a tiny adapter board hosting the particular LCD's connector and its wiring.

- DDR SDRAM, providing memory for the framebuffer, since most smartphone DSI displays don't have one.

- HDMI input: slow version, using FPGA's ISERDES blocks (up to 1080p @ 48 Hz) or a fast one (1080p @ 60 Hz), based on Analog Devices' ADV7611 chip. The external HDMI decoder shares some pins with the SDRAM chip and the host interface, so the full HD - 60 Hz version can only work as a HDMI to DSI adapter.

- Host interface: 12 pins wired to Arduino shield's IOH/IOL headers. Exact functions are not defined yet, I'm thinking about a 4-wire SPI interface and an 8-bit parallel bus.

- USB UART a CP2102 chip providing USB UART, software bootloader and JTAG functionality for the FPGA.

- Main power supply: integrated PMIC (TI/National LM26480). Voltages are: +3.3 V (HDMI input, USB, host I/F), +2.5 V (SDRAM and FPGA Vccaux), +1.8 V (DSI), +1.2 V (FPGA core).

- LCD bias/backlight power suply: Most displays need some higher positive/negative votlage to operate. The board has a simple DC/DC converter for that purpose, producing symmetric voltage of up to +/- 6 V. The voltage can be adjusted for the particular panel by connecting a resistor between one of the DSI connector pins and ground. There is also a separate current driver for backlight LEDs, programmable by another resistor. Both DC/DC converters use a TPS61041 chip.

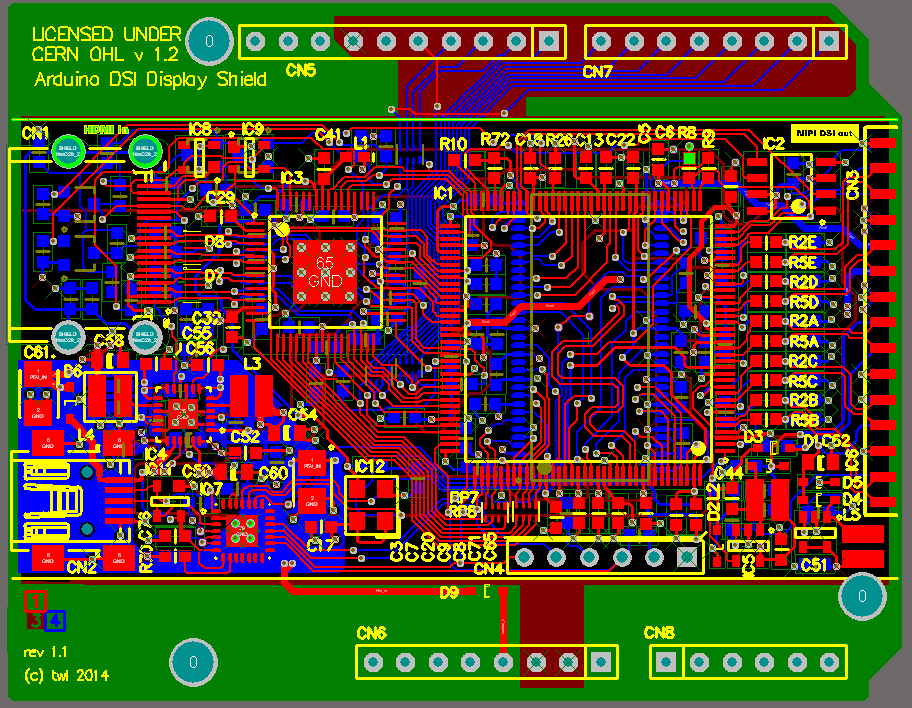

PCB Design

The DSI shield consists of two PCBs - the main board, where all the cool stuff is and a small adapter board, usually different for each display, connected through a 30 pin 2mm pinhead.

The main board is a typical Arduino shield. I routed the design on 4 layers, with the signals on the 2 outer layers, a contiguous ground plane and a split power plane. The DDR is placed right under the FPGA to simplify routing. SSTL to DSI level translator resistors are placed right next to the FPGA output pins to avoid stubs. All differential pairs are calculated for Z0=100 Ohm.

The adapter boards simply route the DSI lanes,...

Read more » twl

twl

István Hegedűs

István Hegedűs

PK

PK

Samuel A. Falvo II

Samuel A. Falvo II

Nick Bild

Nick Bild

Does anyone know if this project can do 1080p/60hz as-is or with some modification to the design? I am confused about the 1080p/48hz (slow ISERDES) and the 1080p/60hz (fast ADV7611) option?

The end goal is to connect a 1080p/60hz display to the Raspberry Pi 4 hdmi port, and drive it at 1080p/60hz.

Any help would be much appreciated, great project overall!